# Lecture Notes in Computer Science Edited by G. Goos, J. Hartmanis and J. van Leeuwen

nce 1781

# Springer Berlin

Berlin

Heidelberg

New York

Barcelona

Hong Kong

London

Milan

Paris

Singapore

Tokyo

# Compiler Construction

9th International Conference, CC 2000 Held as Part of the Joint European Conferences on Theory and Practice of Software, ETAPS 2000 Berlin, Germany, March 25 - April 2, 2000 Proceedings

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

Volume Editor

David A. Watt University of Glasgow Department of Computing Science Glasgow G12 8QQ, Scotland E-mail: daw@dcs.gla.ac.uk

Cataloging-in-Publication Data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

Compiler construction: 9th international conference; proceedings / CC 2000, held as part of the Joint European Conferences on Theory and Practice of Software, ETAPS 2000, Berlin, Germany, March 25 - April 2, 2000 / David A. Watt (ed.). - Berlin; Heidelberg; New York; Barcelona; Hong Kong; London; Milan; Paris; Singapore; Tokyo: Springer, 2000

(Lecture notes in computer science; Vol. 1781)

ISBN 3-540-67263-X

CR Subject Classification (1991): D.3.4, D.3.1, F.4.2, D.2.6, I.2.2

ISSN 0302-9743 ISBN 3-540-67263-X Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag is a company in the BertelsmannSpringer publishing group. © Springer-Verlag Berlin Heidelberg 2000 Printed in Germany

Typesetting: Camera-ready by author, data conversion by DA-TeX Gerd Blumenstein Printed on acid-free paper SPIN 10719928 06/3142 5 4 3 2 1 0

### Foreword

ETAPS 2000 was the third instance of the European Joint Conferences on Theory and Practice of Software. ETAPS is an annual federated conference that was established in 1998 by combining a number of existing and new conferences. This year it comprised five conferences (FOSSACS, FASE, ESOP, CC, TACAS), five satellite workshops (CBS, CMCS, CoFI, GRATRA, INT), seven invited lectures, a panel discussion, and ten tutorials.

The events that comprise ETAPS address various aspects of the system development process, including specification, design, implementation, analysis, and improvement. The languages, methodologies, and tools which support these activities are all well within its scope. Different blends of theory and practice are represented, with an inclination towards theory with a practical motivation on one hand and soundly-based practice on the other. Many of the issues involved in software design apply to systems in general, including hardware systems, and the emphasis on software is not intended to be exclusive.

ETAPS is a loose confederation in which each event retains its own identity, with a separate program committee and independent proceedings. Its format is open-ended, allowing it to grow and evolve as time goes by. Contributed talks and system demonstrations are in synchronized parallel sessions, with invited lectures in plenary sessions. Two of the invited lectures are reserved for "unifying" talks on topics of interest to the whole range of ETAPS attendees. The aim of cramming all this activity into a single one-week meeting is to create a strong magnet for academic and industrial researchers working on topics within its scope, giving them the opportunity to learn about research in related areas, and thereby to foster new and existing links between work in areas that were formerly addressed in separate meetings. The program of ETAPS 2000 included a public business meeting where participants had the opportunity to learn about the present and future organization of ETAPS and to express their opinions about what is bad, what is good, and what might be improved.

ETAPS 2000 was hosted by the Technical University of Berlin and was efficiently organized by the following team:

Bernd Mahr (General Chair)

Hartmut Ehrig (Program Coordination)

Peter Pepper (Organization)

Stefan Jähnichen (Finances)

Radu Popescu-Zeletin (Industrial Relations)

with the assistance of BWO Marketing Service GmbH. The publicity was superbly handled by Doris Fähndrich of the TU Berlin with assistance from the ETAPS publicity chair, Andreas Podelski. Overall planning for ETAPS conferences is the responsibility of the ETAPS steering committee, whose current membership is:

#### VI Foreword

Egidio Astesiano (Genova), Jan Bergstra (Amsterdam), Pierpaolo Degano (Pisa), Hartmut Ehrig (Berlin), José Fiadeiro (Lisbon), Marie-Claude Gaudel (Paris), Susanne Graf (Grenoble), Furio Honsell (Udine), Heinrich Hußmann (Dresden), Stefan Jähnichen (Berlin), Paul Klint (Amsterdam), Tom Maibaum (London), Tiziana Margaria (Dortmund), Ugo Montanari (Pisa), Hanne Riis Nielson (Aarhus), Fernando Orejas (Barcelona), Andreas Podelski (Saarbrücken), David Sands (Göteborg), Don Sannella (Edinburgh), Gert Smolka (Saarbrücken), Bernhard Steffen (Dortmund), Wolfgang Thomas (Aachen), Jerzy Tiuryn (Warsaw), David Watt (Glasgow), Reinhard Wilhelm (Saarbrücken)

#### ETAPS 2000 received generous sponsorship from:

the Institute for Communication and Software Technology of TU Berlin the European Association for Programming Languages and Systems the European Association for Theoretical Computer Science the European Association for Software Development Science the "High-Level Scientific Conferences" component of the European Commission's Fifth Framework Programme

I would like to express my sincere gratitude to all of these people and organizations, the program committee members of the ETAPS conferences, the organizers of the satellite events, the speakers themselves, and finally Springer-Verlag for agreeing to publish the ETAPS proceedings.

January 2000 Donald Sannella ETAPS Steering Committee Chairman

# **Preface**

The International Conference in Compiler Construction (CC) is a forum for presentation and discussion of recent developments in language processors and language design. It emphasizes practical methods and tools. CC 2000 was the ninth conference in the series.

The CC conference originated as a series of workshops organized since 1986 by Günter Riedewald in East Germany. In 1992 the series was relaunched by Uwe Kastens in Paderborn. It was highly appropriate that the first CC conference of the new millennium should take place in Berlin, newly restored as the capital city of reunified Germany.

The CC conference, originally biennial, federated to ETAPS in 1998 and became annual. Despite that major change, the number of submissions and the number of accepted papers have remained stable. The program committee received 46 submissions for CC 2000, from which eighteen high-quality papers were selected for presentation. These papers are included in these proceedings.

The invited speaker at CC 2000 was Reinhard Wilhelm, whose talk was entitled *Shape Analysis*. A paper based on the invited talk opens these proceedings.

The work of the CC 2000 program committee was conducted entirely by electronic means. This made it practicable for all program committee members to participate fully in discussions of individual papers, to re-read papers, and in some cases to provide extra reviews. I believe that the quality of the paper selection process benefited greatly from this mode of working.

I am glad to acknowledge the hard work and friendly cooperation of all my colleagues on the program committee. I also wish to thank the much larger number of additional reviewers who helped us to read and evaluate the submitted papers. As a first-time program chair I have particular reason to appreciate the support and advice of the ETAPS chair, Don Sannella, and of the CC steering committee. Finally, I wish to thank all the authors of submitted papers for their continued interest, without which the CC conference could not thrive.

January 2000 David Watt

# CC Steering Committee

Peter Fritzson (Sweden) Tibor Gyimothi (Hungary) Stefan Jähnichen (Germany) Uwe Kastens (Germany) Kai Koskimies (Finland) David Watt (UK) Reinhard Wilhelm (Germany)

# CC 2000 Program Committee

Rudolf Eigenman (USA) Christine Eisenbeis (France) Christian Ferdinand (Germany) Guang Gao (USA) Görel Hedin (Sweden) Olivier Michel (France) Simon Peyton Jones (UK) Lawrence Rauchwerger (USA)

Mooly Sagiv (Israel)

Helmut Seidl (Germany)

Martin Simons (Germany)

Chau-Wen Tseng (USA)

Bruce Watson (South Africa)

David Watt (UK, chair)

Hans Zima (Austria)

#### CC 2000 Reviewers

Gagan Agrawal José Nelson Amaral Brian Armstrong Denis Barthou Siegfried Benkner Peter Brezany Manuel Chakravarty Jong-Deok Choi Philippe Clauss Albert Cohen Jean-Francois Collard Graham Collins Charles Consel Aino Cornils Ron Cytron Franck Delaplace Nurit Dor Étienne Duris Daniel Étiemble Paul Feautrier Ines Fev Cedric Fournet Jean-Louis Giavitto Manish Gupta David Hanson Paul Havlak Chung-Hsing Hsu François Irigoin

Anders Ive

Alin Jula Daniel Kaestner Richard Kennell Christoph Kessler Seon Wook Kim Torsten Klein Marc Langenbach James Larus Erwin Laure Daniel Lavery Jaejin Lee Xavier Lerov Tal Lev-Ami Wei Li Eva Magnusson Florian Martin Wellington Martins Éduard Mehofer Oege de Moor Rishivur Nikhil Anders Nilsson Rinetskev Noam Preeti Ranjan Panda Sven Panne Insung Park Michael Parkes Jonas Persson Patrik Persson Wolf Pfannenstiel

Sara Porat Jan Prins James Riely Martin Rinard Sven Robertz Erven Rohou Bernhard Scholz Ran Shaham Viera Sipkova Anthony Sloane V.C. Sreedhar Arthur Stoutchinin Doaitse Swierstra Clemens Szyperski Olivier Temam Alexandre Tessier Henrik Theiling Stephan Thesing François Thomasset Michael Voss Philip Wadler David Wakeling Reinhard Wilhelm Eran Yahav Hongbo Yang Pen-Chung Yew Hao Yu Chihong Zhang Wolf Zimmermann

# Table of Contents

| Shape Analysis                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Optimizing Java Bytecode Using the Soot Framework: Is It Feasible? 18 Raja Vallée-Rai, Etienne Gagnon, Laurie Hendren, Patrick Lam, Patrice Pominville and Vijay Sundaresan |

| Pipelined Java Virtual Machine Interpreters                                                                                                                                 |

| Automatic Removal of Array Memory Leaks in Java                                                                                                                             |

| A Static Study of Java Exceptions Using JESP                                                                                                                                |

| Fast Escape Analysis and Stack Allocation for Object-Based Programs 82<br>David Gay and Bjarne Steensgaard                                                                  |

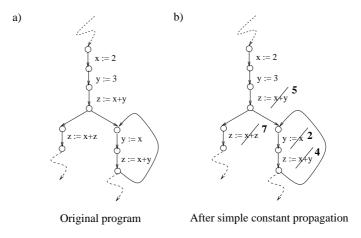

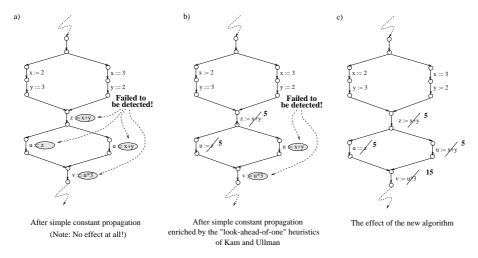

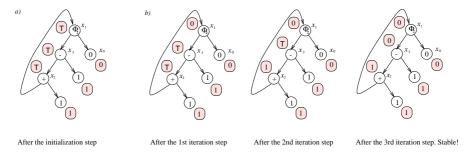

| Constant Propagation on the Value Graph: Simple Constants and Beyond                                                                                                        |

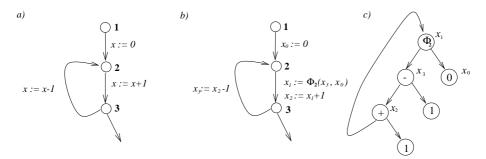

| Simple Generation of Static Single-Assignment Form                                                                                                                          |

| Demand-Driven Construction of Call Graphs                                                                                                                                   |

| A Framework for Loop Distribution on Limited On-Chip Memory Processors                                                                                                      |

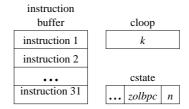

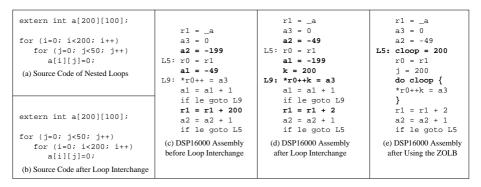

| Techniques for Effectively Exploiting a Zero Overhead Loop Buffer157 Gang-Ryung Uh, Yuhong Wang, David Whalley, Sanjay Jinturkar, Chris Burns and Vincent Cao               |

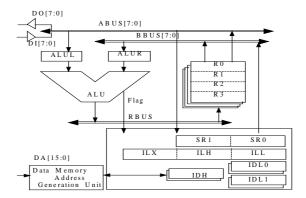

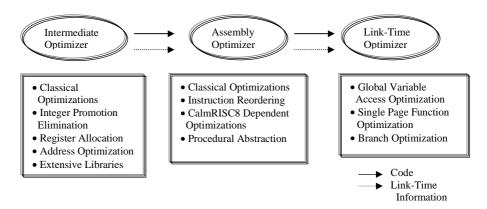

| Advanced Compiler Optimization for CalmRISC8 Low-End Embedded Processor                                                                                                     |

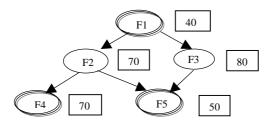

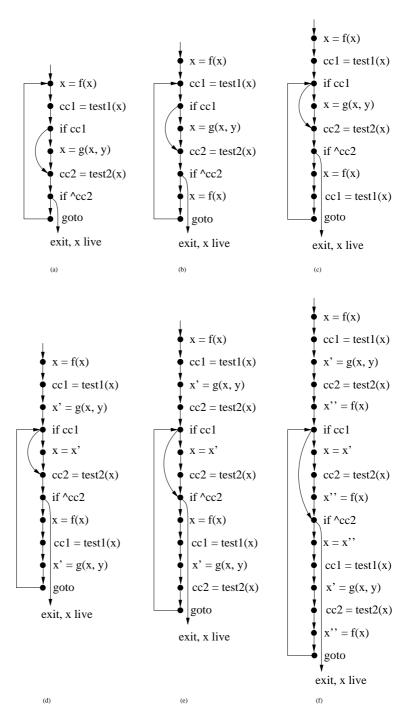

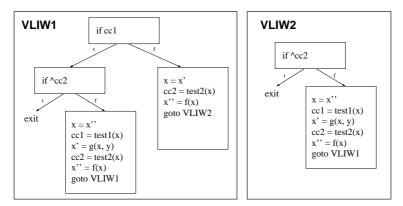

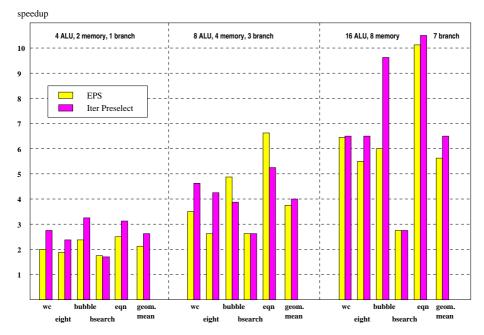

| Global Software Pipelining with Iteration Preselection                                                                                                                      |

| Analysis of Irregular Single-Indexed Array Accesses and Its Applications in Compiler Optimizations                                                                          |

# X Table of Contents

| Advanced Scalarization of Array Syntax                                                                  |

|---------------------------------------------------------------------------------------------------------|

| Techniques for Reducing the Overhead of Run-Time Parallelization 232<br>Hao Yu and Lawrence Rauchwerger |

| MATOU: An Implementation of Mode–Automata249 Florence Maraninchi, Yann Rémond and Yannick Raoul         |

| Compiling Adaptive Programs by Partial Evaluation                                                       |

| Functional Incremental Attribute Evaluation                                                             |

| Author Index                                                                                            |

# Shape Analysis

Reinhard Wilhelm<sup>1</sup>, Mooly Sagiv<sup>2</sup>, and Thomas Reps<sup>3</sup>

Fachbereich Informatik, Universität des Saarlandes

Department of Computer Science, Tel-Aviv University

Computer Science Department, University of Wisconsin at Madison

**Abstract.** A shape-analysis algorithm statically analyzes a program to determine information about the heap-allocated data structures that the program manipulates. The results can be used to understand or verify programs. They also contain information valuable for debugging, compile-time garbage collection, instruction scheduling, and parallelization.

#### 1 Introduction

Pointers and anonymous objects stored in the heap seem to be the dark corner of imperative programming languages. There are only a few treatments of the semantics of pointers. Most semantic descriptions of imperative programming languages even assume the nonexistence of pointers, since otherwise the semantics of an assignment statement becomes much more complex. The reason is that an assignment through a pointer variable or pointer component may have far reaching side-effects.

These far reaching side-effects also make program dependence analysis harder, since they make it difficult to compute the aliasing relationships among different pointer expressions in a program. Having less precise program dependence information decreases the opportunities for automatic parallelization and for instruction scheduling.

The usage of pointers is error prone. Dereferencing NULL pointers and accessing previously deallocated storage are two common programming mistakes. The usage of pointers in programs is thus an obstacle for program understanding, debugging, and optimization. These activities need answers to many questions about the structure of the heap contents and the pointer variables pointing into the heap.

Shape analysis is a generic term denoting static program-analysis techniques attempting to determine properties of the heap contents relevant for the applications mentioned above.

#### 1.1 Structure of the Paper

The structure of the paper is as follows: In Section 2, a number of questions about the contents of the heap are listed. Subsection 2.1 presents a program that will

be used as a running example, a program that destructively reverses a singly linked list. Subsection 2.2 shows how shape analysis would answer the questions about the heap contents produced by this program. Section 3 then introduces a parametric shape analysis along the lines of [23], which provides for a generative way to design and implement shape-analysis algorithms. The "shape semantics" plus some additional properties that individual storage elements may or may not possess are specified in logic, and the shape-analysis algorithm is automatically generated from such a specification. Throughout the paper, abstraction functions and transfer functions are given intuitively, by means of examples. Section 4 presents experience obtained via an implementation done in Java. Section 5 briefly discusses related work. Section 6 presents some conclusions.

# 2 Questions About the Heap Contents

Shape analysis has a somewhat constrained view of programs. It is not interested in numerical or string values that programs compute, but exclusively in the linked structures they build in the heap and in the pointers into the heap from the stack, from global memory, or from cells in the heap. We will therefore use the term execution state to mean the set of cells in the heap and their connectivity by pointer components of heap cells and the values of pointer variables in the store.

Among the questions about execution states that we might wish to pose at points in a program are:

**NULL-pointers:** May a pointer variable or a pointer component of a heap cell contain NULL? This is valuable debugging information at the entry of a statement attempting to dereference this pointer.

May-Alias: May two pointer expressions reference the same heap cell? The absence of may-aliasing can be used for improving program dependence information [3,20].

Must-Alias: Will two pointer expressions always denote the same heap cell? This may be used to predict a cache hit or to trigger a prefetch.

Sharing: May a heap cell be shared?<sup>1</sup> There are many uses for such information. Explicit deallocation of a shared node may leave the storage manager in an inconsistent state (e.g., if the heap cell is deallocated twice – by calls on the deallocator at each predecessor). A nonshared cell may be explicitly deallocated when the last pointer to it ceases to exist. This again is valuable for debugging.

**Reachability:** Is a heap cell reachable from a specific variable or from any pointer variable? Unreachable cells are certainly garbage.

**Disjointness:** Will two data structures pointed to by two distinct pointer variables ever have common elements? Disjoint data structures may be processed in parallel by different processors and may be stored in different memories [8].

<sup>&</sup>lt;sup>1</sup> Later on in the paper the term "shared" means "heap-shared" i.e., pointed to by two or more pointer components of heap cells. Sharing due to two pointer variables or one pointer variable and one heap cell component pointing to the same heap cell is also deducible from the results of shape analysis.

**Cyclicity:** May a heap cell be part of a cycle? If not, garbage collection could be done by reference counting.

**Shape:** What will be the "shape" of (some part of) the heap contents? Shapes (or, more precisely, shape descriptors) characterize data structures. A shape descriptor could indicate whether the heap contains a singly linked list, potentially with/definitely without a cycle, a doubly linked list, a binary tree, etc. Many of the properties listed above are ingredients of shape analyses, e.g., sharing, cyclicity, reachability, disjointness.

Shape analysis can be understood as an extended type analysis; its results can be used as an aid in program understanding, debugging [6], and verification.

#### 2.1 An Example: Destructive Reverse

The following program, reverse, is used as a running example. It destructively reverses a list pointed to by x into one pointed to by y.

```

/* reverse.c */

#include "list.h"

List reverse(List x) {

List y, t;

y = NULL;

while (x != NULL) {

t = y;

y = x;

x = x->n;

y->n = NULL;

y->n = t;

}

return y;

}

```

It assumes the declaration of a List data type

```

/* list.h */

typedef struct node {

struct node *n;

int data;

} *List

```

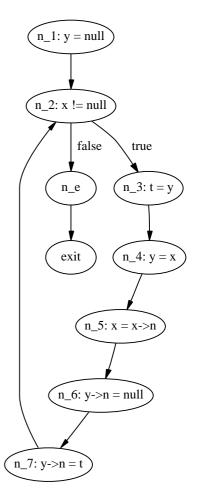

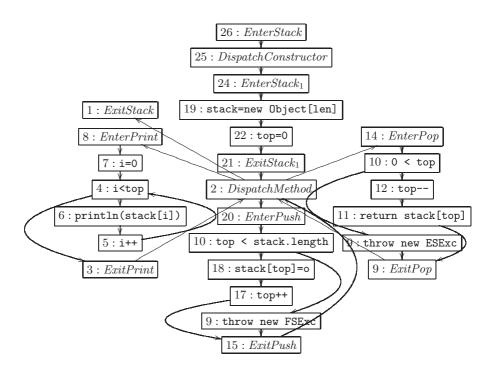

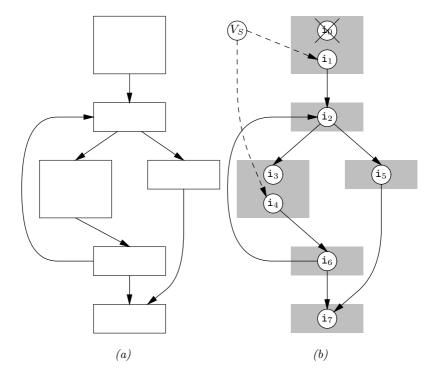

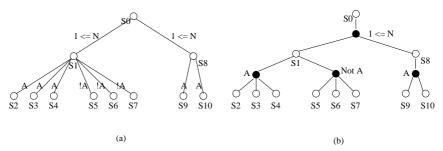

The control flow graph of reverse is reproduced in Fig. 1. The program points are labeled for ease of reference. The body of the loop does the following: Pointer variable tholds on to the current y-list (n\_3), while y

Fig. 1. Flow graph of a list-reversal program

#### 4 Reinhard Wilhelm et al.

grabs the head of the current x-list  $(n_4)$ . x is then moved to the tail of the current x-list  $(n_5)$ . y->n is first nulllified  $(n_6)$  and then made to connect the new head to the old y-list  $(n_7)^2$ .

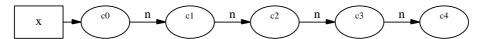

Fig. 2. An input list for reverse

The workings of reverse is exemplified on the input list shown in Fig. 2. Table 1 shows the execution state after n\_3 during the first four iterations of the loop.

Let us assume that the input to this program will be a non-empty acyclic singly linked list made up of unshared elements like the one shown in Fig. 2. Some correct answers to the questions listed in Section 2 would be:

#### after n\_3:

- x and y point to acyclic singly linked lists; the y-list may be empty,

- t and y are may- and must-aliases or both point to NULL.

- x never points to NULL,

- the lists to which x and y point are disjoint,

- no list element is heap-shared.

after n\_4: x and y are must-aliases, and therefore also may-aliases.

after  $n_5$ : x and y are not may-aliases, and therefore not must-aliases. (Note that this would not be the case if the initial x-list contained a cycle).

everywhere: there are no garbage cells.

#### 2.2 Answers as Given by Shape Analysis

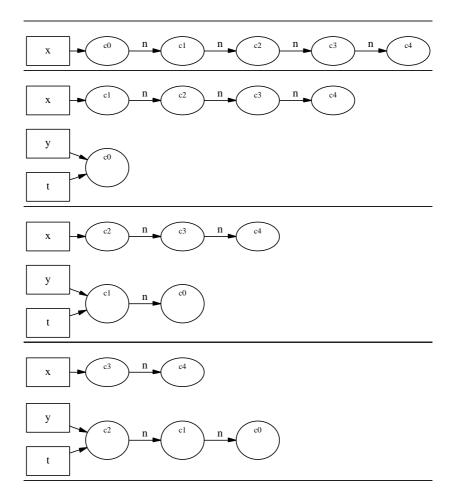

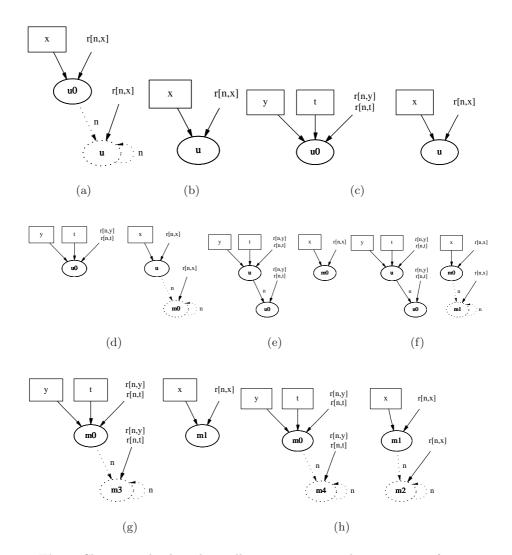

Shape analysis will be started under the aforementioned assumption that the input to the program will be a non-empty acyclic singly linked list. This is expressed by the so-called shape graphs shown in Fig. 3.

Shape analysis of reverse will produce information for each program point about the lists that can arise there. For program point n\_3, the results would be given as the shape graphs shown in Fig. 4.

These graphs should be interpreted as follows:

A rectangular box containing the name p represents pointer variable p. The

pointer variables of program reverse, namely x, y, and t, appear boxed in

the shape graphs in Figures 3 and 4.

<sup>&</sup>lt;sup>2</sup> Splitting this assignment into two steps is done to simplify the definition of the semantics.

Table 1. The first four iterations of the loop in reverse after n\_3

- Ovals stand for abstract locations. A solid oval stands for an abstract location that represents exactly one heap cell. In Fig. 3(b), the oval u represents the one cell of an input list of length 1.

- A dotted oval box stands for an abstract location that may represent one or more heap cells; in Fig. 3(a) the dotted oval u represents the cells in the tail of the input list. In the example input list shown in Fig. 2, these are the cells c1, c2, c3, and c4.

- A solid edge labeled c between abstract locations m and m' represents the fact that the c-component of the heap cell represented by m will point to the heap cell represented by m'. Fig. 4(e) indicates that the n-component of the heap cell represented by u will point to the heap cell represented by u0.

**Fig. 3.** A description of the input to reverse. (a) represents acyclic lists of length at least 2, (b) lists of length 1.

This edge represents the n-component of c1 pointing to c0 in the third figure in Table 1.

- A dotted edge labeled c between abstract locations m and m' tells us that the c-component of one of the heap cells represented by m may point to one of the heap cells represented by m'. In the case when m and m' are the same abstract location, this edge may or may not represent a cycle. In Fig. 4(d), the dotted self-cycle on location m0 represents n-components of heap cells represented by m0 possibly pointing to other heap cells represented by m0. Additional information about non-heap-sharing (see below) implies that, in this case, the dotted self-cycle does not represent a cycle in the heap.

- Fig. 4(d) represents the execution state of the second figure in Table 1. The dotted location m0 represents the heap cells c2, c3, c4; the dotted n-back-edge represents the two pointers from c2 to c3 and from c3 to c4, respectively.

- Other solid edges to an abstract location m represent properties that are definitely possesed by the heap cells represented by m. For example, a solid edge from a pointer variable p to m represents the fact that p will point to the heap cell represented by m, i.e., this heap cell will have the property "pointed-to-by-p". Another property in the example is "reachable-from-x-through-n", denoted in the graph by r[n,x]. It means that the heap cells represented by the corresponding abstract location are (transitively) reachable from pointer variable x through n-components.

- Solid ovals could be viewed as abstract locations having the property "uniquely representing", later on called "not-summarized".

- A dotted edge from a property to an abstract location indicates that the heap cells represented by that location may or may not have that property.

- The absence of an edge from a property to an abstract location m means that the heap cells represented by m definitely do not have this property. In Fig. 4(a), the absence of an edge from y to the location u0 means that y will definitely not point to the cell represented by u0. The absence of a

Fig. 4. Shape graphs describing all execution states that can arise after n\_3

pointer variable p in a shape graph means that in the stores represented by this graph p points to NULL.

In the analysis of reverse, a very important heap cell property is is which means "is (heap-)shared". It does not show up in any of the graphs in Fig. 4, signifying that no heap cell is be shared in any of the execution states that can arise after n\_3.

In summary, the shape graphs portray information of three kinds:

**solid** meaning "always holds" for properties (including "uniquely representing"),

absent meaning "never holds" for properties, and

dotted meaning "don't know" for properties (including "uniquely representing"),

In the following, "always holds" and "never holds" will be called *definite* values of properties, while "don't know" will be called the *indefinite* value.

Each shape graph produced at some program point describes execution states that could occur when execution reaches that program point. The set of all graphs produced at some program point describes (a superset of) all the execution states that can occur whenever execution reaches that program point.

With this interpretation in mind, all the claims about the properties of the heap contents after n<sub>-</sub>3 can be checked by verifying that they hold on all of the graphs shown in Fig. 4.

# 3 Shape Analysis

The example program reverse works for lists of arbitrary lengths. However, as was described in the preceding section (at least for one program point), the description of the lists occurring during execution is finite: there are 8 graphs describing all x- and y-lists arising after n\_3. This is a general requirement for shape analysis. While the data structures that a program builds or manipulates are in general of unbounded size, their shape descriptor has to have a bounded size.

This representation of the heap contents has to be *conservative* in the sense that whoever asks for properties of the heap contents—e.g., a compiler, a debugger, or a program understanding system—receives a reliable answer. The claim that "pointer variable p or pointer component  $p \rightarrow c$  never has the value NULL at this program point" may only be made if indeed this is the case for all executions of the program and all program paths leading to the program point. It may still be the case that in no program execution p (resp.  $p \rightarrow c$ ) will be NULL at this point, but that the analysis will be unable to derive this information. In the field of program analysis, we say that program analysis is allowed to (only) "err on the safe side."

In short, shape analysis computes for a given program and each point in the program:

a finite, conservative representation of the heap-allocated data structures that could arise when a path to this program point is executed.

#### 3.1 Summarization

The constraint that we must work with a bounded representation implies a loss of information about the heap contents. Size information, such as the lengths of

lists or the depths of trees, will in general be lost. However, structural information may also get lost due to the chosen representation. Thus, there is a part of the execution state (or some of its properties) that is exactly represented, and some part of the execution state (or some of its properties) that is only approximatively represented. The process leading to the latter is called *summarization*. Summarization intuitively means the following:

- Some heap cells will "lose their identity", i.e., will be represented together with other heap cells by one abstract location.

- The connectivity among those jointly represented heap cells will be represented conservatively, i.e., each pointer in the heap will be represented, but several such pointers (or the absence of such pointers) may be represented jointly.

- Properties of these heap cells will also be represented conservatively. This

means the following:

- a property that holds for all (for none of the) summarized cells will be found to hold (not to hold) for their summary location,

- a property that holds for some but not all of the summarized cells will have the value "don't know" for the summary location.

As will be seen in Subsection 3.5, one of the main problems is how to extract an abstract location from a summary location when (in a concrete execution of the program) a pointer is advanced to one of the heap cells represented by this summary location. This process will be called "materializing a new abstract location out of a summary location".

#### 3.2 Static Program Analysis

Shape analysis is a *static program analysis* technique. It can thus be couched in terms of the theory of *Abstract Interpretation*, cf. [4,17]. The most important ingredient of any static program analysis is an *abstraction function*. The abstraction function relates two worlds: in the case of shape analysis, the *concrete world* of program execution states and the *abstract world* of shape graphs. It maps an execution state to its bounded, conservative representation. The abstraction function does what is described as summarization above.

The concrete semantics of the programming language is given by a set of functions  $f_{st}$  for each statement st of the language. They describe the effect of the statements on an execution state. The abstract semantics describes the effect of the statements on the representation of execution states. It is given in the form of an abstract transfer function  $f_{st}^{\#}$  for each statement st. Applying  $f_{st}^{\#}$  will be called abstractly executing st.

#### 3.3 Parametric Shape Analysis

"Shape analysis" is a generic term standing for a whole class of algorithms of different power and complexity trying to answer questions about structures in the heap. In our setting, a particular shape-analysis algorithm is determined by a set of properties that heap cells may have (and whose values will be tracked by the shape-analysis algorithm).

First, there are the *core properties*, e.g., the "pointed-to-by-p"-property for each program pointer variable p and the property "connected-through-c", which pairs of heap cells  $(l_1, l_2)$  possess if the c-component of  $l_1$  points to  $l_2$ . These properties are part of any pointer semantics. The core properties in the particular shape analysis of the **reverse** program are "pointed-to-by-x", denoted just by x, "pointed-to-by-y", denoted by y, and "pointed-to-by-t", denoted by t, and "connected-through-n" denoted by n.

Further properties are called *instrumentation properties* [23]. They are determined by what the analysis is meant to observe. They are expressed in terms of the core properties. Our example analysis should find out properties of programs manipulating acyclic singly linked lists. Sharing properties are important to detect acyclicity. Reachability properties from specific pointer variables are important to keep disjoint sublists summarized separately when a pointer moves through a list.

Therefore, the instrumentation properties in our example analysis are "isheap-shared", denoted by is, "reachable-from-x-through-n", denoted by r[n,x], "reachable-from-y-through-n", denoted by r[n,y], and "reachable-from-t-through-n", denoted by r[n,t]. A property existing in every shape analysis is "not-summarized".

#### 3.4 Abstraction Functions

The abstraction function of a particular shape analysis is determined by a subset of the set of all properties, the so-called *abstraction properties*.<sup>3</sup> The principle is that heap cells that have the same definite values for the abstraction properties are summarized to the same abstract location. Thus, if we view the set of abstraction properties as our means of observing the contents of the heap, the heap cells summarized by one summary location have no observable difference.

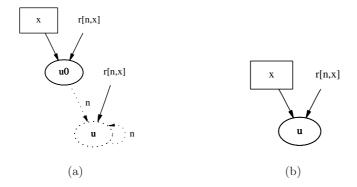

In Fig. 3(a), all the cells in the tail of an input list of length at least two are summarized by the abstract location u, since they all have the property r[n,x] and do not have the properties x, y, t, r[n,y], r[n,t], is. The abstract location u0 represents exactly the first cell of the input list. It has the properties x and r[n,x] and none of the other properties.

#### 3.5 Analyzing a Statement

An abstract semantics of the pointer statements available in the language has to be specified in some formalism. It describes how the core and the instrumentation properties change when a statement is executed.

The most complex statement involving pointers is the one that moves a pointer along a pointer component. In the reverse program there is one such statement, n\_5: x=x->n. Its semantics will be described by means of an example.

<sup>&</sup>lt;sup>3</sup> [23] uses only unary properties.

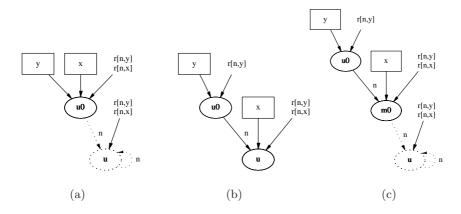

The shape graph in Fig. 5(a) describes some of the lists that can arise before program point n<sub>-</sub>5.

Fig. 5. (a): A shape graph that arises before n\_5; (b) and (c): the two shape graphs resulting from (abstractly) executing x=x->n on shape graph (a).

At n\_5 the statement x=x->n is (abstractly) executed. One candidate result might be the shape graph in which x has moved along the indefinite edge labeled n to point to the abstract location u. However, this would not be an acceptable shape graph, since it is not in the image of the abstraction function. To see this, note that a summarized abstract location representing one or more heap cells cannot have the definite property "pointed-to-by-x". The semantics of C (as well as of other languages with pointers) implies that any pointer variable or pointer component can only point to at most one cell at any one time. Hence, only two cases are possible: (i) x points to NULL, or (ii) x points to exactly one cell.

A better approach to creating the shape graph that results from (abstractly) executing x=x-n is to do a case analysis of the reasons why u's "not-summarized" property and the two n-edges are indefinite.

- The first case assumes that a definite n-edge exists starting at u0, and that u represents exactly one heap cell. What about the indefinite trivial cycle labeled n on u? The absence of an is-edge to u indicates that the cell represented by u is not shared. Thus, the back-edge from u to u in Fig. 5(a) cannot represent a concrete back pointer, since there is already one solid edge to u representing a concrete pointer. Hence, the indefinite back-edge from u to u has to be eliminated. The abstract execution of the statement x=x->n results in the graph shown in Fig. 5(b).

- The second case also assumes that a definite n-edge exists starting at u0. However, we now assume that u represents more than one heap cell. A new definite abstract location, called m0, is then "materialized" out of u. It represents the first of the cells in the tail of the x/y-list. The definite edge starting

at u0 is made to point to it. The argumentation about a potential back-edge to it is the same as in the first case: the newly materialized location does not have the property is and thus cannot be the target of a back-edge. The execution of the statement x=x-n results in the graph shown in Fig. 5(c).

A third case would have the indefinite n-edge representing the absence of a pointer from the cell represented by u0 to any of the cells represented by u. However, this is incompatible with the fact that the r[n,x] and r[n,y] properties of u have the (definite) value 1. Hence, this case is impossible.

The less powerful a shape analysis is, the more information about the heap contents will in general be summarized. Most shape-analysis algorithms are exponential or even doubly exponential in some parameters derived from the program and some parameters determined by the set of properties to be observed.

# 4 Implementation and Experience

The three-valued-logics approach described in this paper has been implemented in the TVLA-engine (Three-Valued Logic Analysis) by Tal Lev-Ami at Tel-Aviv University [16]. This prototype implementation in Java is good for experimenting with analysis designs. Small examples like reverse can be analyzed in a few seconds on a Pentium 166 MHz PC. Bigger examples, e.g., Mobile Ambients [18], may take several hours.

A surprising experience was the following: Although one expects that a more precise analysis is more costly in terms of time and space, this is not necessarily true in three-valued logic based analyses: A more precise analysis may create fewer unneeded structures and thus run faster. For instance, Lev-Ami analyzed a program to sort the elements of a linked list. When a list-merge function was analyzed without reachability properties, the analysis created tens of thousands of graphs such that the machine ran out of space. Adding reachability properties reduced the number of graphs to 327 and the analysis time to 8 seconds.

A number of issues need to be addressed for the TVLA-engine to become a useful tool for large programs.

#### 5 Related Work

Only a very brief account of related work can be given in this paper. A more detailed treatment is given in [22].

#### 5.1 Types and Allocation Sites

One of the earliest properties of heap cells used for abstraction has been the point in the program at which the cells were allocated, i.e., their *allocation site* [12,2,24,1,19]. Cells allocated at different program points would never be represented jointly by one node. The motivation behind this approach was that

"nodes allocated in different places probably are going to be treated differently, while all nodes allocated at a given place will probably be updated similarly" [2].

This is sometimes true and sometimes not true. For example, allocation-site information fails to keep abstract locations separate when all cells of a data structure are allocated at the same program point.

The methods described above use additional information such as sharing or heap reference counts to improve the precision of the results.

Types have also been used to partition the set of heap cells. In a typed language, a typed pointer may only point to cells of the appropriate type. They could be used if nothing else is available. However, they will lead only to very coarse representations because often all cells of a data structure have the same type.

Both allocation-site information and type information induce a static partition on the heap. This is in contrast with the approach described above, which induces a dynamic partition on the heap.

#### 5.2 Pointer Variables

[25,21,22] used only the "pointed-to-by-p" properties to define the abstraction function. Additional information such as non-sharing information was used to improve precision. The algorithm given in [21,22] was the first to achieve strong nullification and strong update of pointer values for statements that modified pointer values. This means, the algorithm could delete or overwrite existing pointers in a conservative way. As a result it was able to materialize new nodes out of summary nodes as described in Section 3.5.

For efficiency reasons, the method presented in [21,22] (as well as the methods described in [12,15,14,2,24]) merged all the information available at a program point into one shape graph. This made the semantics hard to understand and implied a loss in precision. A more precise variant of this method (which is also easier to understand) is described in [17]. It uses sets of shape graphs at each program point.

#### 5.3 k-Bounded Approaches

Another approach to represent unbounded structures in a bounded fashion is to choose a constant k and to represent everything "within a diameter k" precisely and to summarize heap cells outside of this diameter. Applied to our problem of shape analysis, this would mean representing lists precisely up to a length of k, trees up to a depth of k, and general graphs up to a diameter of k, and then summarizing the rest of the data structure. The approach of [11] corresponds to using the "reachable-from-p-via-access-path- $\alpha$ "-property with  $|\alpha| \leq k$ .

The Jones-Muchnick formulation has two drawbacks:

The analysis yields poor results for programs that manipulate cons-cells beyond the k-horizon. For example, for the list-reversal program reverse, little useful information is obtained. The analysis algorithm must model what happens when the program is applied to lists of lengths greater than k. However, the tail of such a list is treated conservatively, i.e., as an arbitrary, and possibly cyclic, data structure.

- The analysis may be extremely costly because the number of possible shapegraphs is doubly exponential in k.

In addition to Jones and Muchnick's work, k-limiting has also been used in a number of subsequent papers (e.g., [10]).

#### 5.4 Methods Not Based on Shape Graphs

There are also several algorithms for finding may-alias information for pointer variables that are not based on shape-graphs. The most sophisticated ones are those of Landi and Ryder [13] and Deutsch [5]. For certain programs that manipulate lists, Deutsch's algorithm offers a way of representing the exact (infinite set of) may aliases in a compact way.

A different approach was taken by Hendren and Nicolau, who designed an algorithm that handles only acyclic data structures [9,7].

#### 6 Conclusions

We conclude with a few general observations.

#### 6.1 A Parametric Framework for Shape Analysis

The method that has been surveyed in this paper provides the basis for a parametric framework for shape analysis. Such a framework has two parts: (i) a language for specifying various properties that a heap cell may or may not possess, and how these properties are affected by the execution of the different kinds of statements in the programming language, and (ii) a method for generating a shape-analysis algorithm from such a description. The first is an issue having to do with specification; the specified set of properties determines the characteristics of the data-structure elements that the static analysis can distinguish. The second is an issue of how to generate an appropriate algorithm from the specification. The ideal is to have a fully automatic method—a yacc for shape analysis, so to speak: The "designer" of a shape-analysis algorithm supplies only the specification, and the shape-analysis algorithm is created automatically from this specification. The TVLA system discussed in Section 4 implements such a parametric framework.

Different instantiations of the framework create analyses that use different classes of shape graphs, and hence are prepared to identify different classes of store properties that hold at the different points in a program. Different classes of shape graphs may be needed, depending on the kinds of linked data structures used in a program and on the link-rearrangement operations performed by the program's statements. (In general, an instantiation of the framework will handle

every program, but may produce conservative results due to the use of a class of shape graphs that does not make appropriate distinctions.) The essence of the particular shape-analysis methods discussed in Section 5 can be captured via different instantiations of the framework.

The instantiation of the analysis framework described in Subsection 3.3 is sufficiently powerful to successfully analyze the reverse program, which works on singly linked lists. It would also produce precise information on many other programs that deal with singly linked lists. However, it would fail on programs that operate on doubly linked lists, since the is-property would hold on all but the first and the last elements of such lists. An instantiation for doubly linked lists would need the following two properties:

**forward-backward-pairing:** If the forward-pointer of a heap cell c1 points to a heap cell c2, then the backward-pointer of c2 must point to c1.

**backward-forward-pairing:** If the backward-pointer of a heap cell c1 points to a heap cell c2, then the forward-pointer of c2 must point to c1.

Different versions of doubly linked lists would need some additional properties for the first and last elements, e.g., requiring that the "unused" pointer has the value NULL.

#### 6.2 Biased Versus Unbiased Static Program Analysis

Many of the classical dataflow-analysis algorithms use bit vectors to represent the characteristic functions of set-valued dataflow values. This corresponds to a logical interpretation (in the abstract semantics) that uses two values. It is definite on one of the bit values and conservative on the other. That is, either "false" means "false" and "true" means "may be true/may be false, or "true" means "true" and "false" means "may be true/may be false". Many other staticanalysis algorithms have a similar character.

Conventional wisdom holds that static analysis must inherently have such a one-sided bias. However, the material developed in [23] shows that while *indefiniteness* is inherent (i.e., a static analysis is unable, in general, to give a definite answer), one-sidedness is not: By basing the abstract semantics on 3-valued logic, definite truth and definite falseness can both be tracked, with the third value capturing indefiniteness.

This outlook provides some insight into the true nature of the values that arise in other static analyses:

- A one-sided analysis that is precise with respect to "false" and conservative with respect to "true" is really a 3-valued analysis over false, true, and "don't know" that conflates true and don't know (and uses "true" in place of don't know).

- Likewise, an analysis that is precise with respect to "true" and conservative with respect to "false" is really a 3-valued analysis over false, true, and "don't know" that conflates false and don't know (and uses "false" in place of don't know).

In contrast, the shape-analysis work has shown how to create analyses that are unbiased: They are precise with respect to both false and true, and use a separate "don't know" value to capture indefiniteness.

# Acknowledgements

Tal Lev-Ami carried out the implementation of TVLA. One instantiation of TVLA was used to analyze the example program and generate the figures used in the paper. Hanne Riis Nielson provided very helpful comments.

#### References

- U. Assmann and M. Weinhardt. Interprocedural heap analysis for parallelizing imperative programs. In W. K. Giloi, S. Jähnichen, and B. D. Shriver, editors, Programming Models For Massively Parallel Computers, pages 74–82, Washington, DC, September 1993. IEEE Press. 12

- D.R. Chase, M. Wegman, and F. Zadeck. Analysis of pointers and structures. In SIGPLAN Conf. on Prog. Lang. Design and Impl., pages 296–310, New York, NY, 1990. ACM Press. 12, 13

- F. Corbera, R. Asenjo, and E.L. Zapata. New shape analysis techniques for automatic parallelization of C code. In *International Computing Symposium*, 1999.

- P. Cousot and R. Cousot. Abstract interpretation: A unified lattice model for static analysis of programs by construction of approximation of fixed points. In Symp. on Princ. of Prog. Lang., pages 238–252, New York, NY, 1977. ACM Press.

- A. Deutsch. Interprocedural may-alias analysis for pointers: Beyond k-limiting. In SIGPLAN Conf. on Prog. Lang. Design and Impl., pages 230–241, New York, NY, 1994. ACM Press. 14

- 6. N. Dor, M. Rodeh, and M. Sagiv. Detecting memory errors via static pointer analysis. In *Proceedings of the ACM SIGPLAN-SIGSOFT Workshop on Program Analysis for Software Tools and Engineering (PASTE'98)*, pages 27–34, June 1998. Available at "http://www.math.tau.ac.il/~ nurr/paste98.ps.gz". 3

- L. Hendren. Parallelizing Programs with Recursive Data Structures. PhD thesis, Cornell Univ., Ithaca, NY, Jan 1990.

- 8. L. Hendren, J. Hummel, and A. Nicolau. Abstractions for recursive pointer data structures: Improving the analysis and the transformation of imperative programs. In SIGPLAN Conf. on Prog. Lang. Design and Impl., pages 249–260, New York, NY, June 1992. ACM Press. 2

- 9. L. Hendren and A. Nicolau. Parallelizing programs with recursive data structures. *IEEE Trans. on Par. and Dist. Syst.*, 1(1):35–47, January 1990. 14

- S. Horwitz, P. Pfeiffer, and T. Reps. Dependence analysis for pointer variables. In SIGPLAN Conf. on Prog. Lang. Design and Impl., pages 28–40, New York, NY, 1989. ACM Press. 14

- N.D. Jones and S.S. Muchnick. Flow analysis and optimization of Lisp-like structures. In S.S. Muchnick and N.D. Jones, editors, *Program Flow Analysis: Theory and Applications*, chapter 4, pages 102–131. Prentice-Hall, Englewood Cliffs, NJ, 1981. 13

- 12. N.D. Jones and S.S. Muchnick. A flexible approach to interprocedural data flow analysis and programs with recursive data structures. In *Symp. on Princ. of Prog. Lang.*, pages 66–74, New York, NY, 1982. ACM Press. 12, 13

- W. Landi and B.G. Ryder. Pointer induced aliasing: A problem classification. In Symp. on Princ. of Prog. Lang., pages 93–103, New York, NY, January 1991. ACM Press. 14

- J.R. Larus. Restructuring Symbolic Programs for Concurrent Execution on Multiprocessors. PhD thesis, Univ. of Calif., Berkeley, CA, May 1989.

- J.R. Larus and P.N. Hilfinger. Detecting conflicts between structure accesses. In SIGPLAN Conf. on Prog. Lang. Design and Impl., pages 21–34, New York, NY, 1988. ACM Press. 13

- T. Lev-Ami. TVLA: A framework for Kleene based static analysis. Master's thesis, 2000. 12

- F. Nielson, H. Riis Nielson, and C. Hankin. Principles of Program Analysis. Springer Verlag, 1999. 9, 13

- F. Nielson, H. Riis Nielson, and M. Sagiv. A Kleene analysis of mobile ambients. In Proceedings of ESOP'2000, 2000.

- J. Plevyak, A.A. Chien, and V. Karamcheti. Analysis of dynamic structures for efficient parallel execution. In U. Banerjee, D. Gelernter, A. Nicolau, and D. Padua, editors, *Languages and Compilers for Parallel Computing*, volume 768 of *Lec. Notes* in Comp. Sci., pages 37–57, Portland, OR, August 1993. Springer-Verlag.

- 20. J.L. Ross and M. Sagiv. Building a bridge between pointer aliases and program dependences. In *Proceedings of the 1998 European Symposium On Programming*, pages 221–235, March 1998. Available at "http://www.math.tau.ac.il/ $\sim$  sagiv". 2

- M. Sagiv, T. Reps, and R. Wilhelm. Solving shape-analysis problems in languages with destructive updating. In Symp. on Princ. of Prog. Lang., New York, NY, January 1996. ACM Press. 13

- 22. M. Sagiv, T. Reps, and R. Wilhelm. Solving shape-analysis problems in languages with destructive updating. *Trans. on Prog. Lang. and Syst.*, 20(1):1–50, January 1998. 12, 13

- 23. M. Sagiv, T. Reps, and R. Wilhelm. Parametric shape analysis via 3-valued logic. In *Symp. on Princ. of Prog. Lang.*, 1999. Available at "http://www.cs.wisc.edu/wpis/papers/popl99.ps". 2, 10, 15

- 24. J. Stransky. A lattice for abstract interpretation of dynamic (Lisp-like) structures. *Inf. and Comp.*, 101(1):70–102, Nov. 1992. 12, 13

- E. Y.-B. Wang. Analysis of Recursive Types in an Imperative Language. PhD thesis, Univ. of Calif., Berkeley, CA, 1994.

# Optimizing Java Bytecode Using the Soot Framework: Is It Feasible?

Raja Vallée-Rai, Etienne Gagnon, Laurie Hendren, Patrick Lam, Patrice Pominville, and Vijay Sundaresan

Sable Research Group, School of Computer Science

McGill University

{rvalleerai,gagnon,hendren,plam,patrice}@sable.mcgill.ca

vijaysun@ca.ibm.com

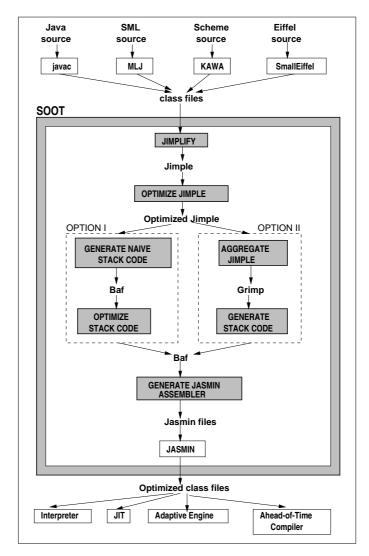

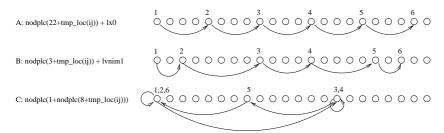

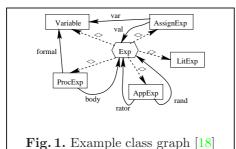

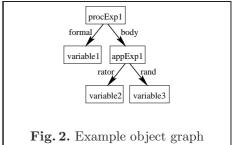

Abstract. This paper presents Soot, a framework for optimizing Java<sup>TM</sup> bytecode. The framework is implemented in Java and supports three intermediate representations for representing Java bytecode: Baf, a streamlined representation of Java's stack-based bytecode; Jimple, a typed three-address intermediate representation suitable for optimization; and Grimp, an aggregated version of Jimple.

Our approach to class file optimization is to first convert the stack-based bytecode into Jimple, a three-address form more amenable to traditional program optimization, and then convert the optimized Jimple back to bytecode.

In order to demonstrate that our approach is feasible, we present experimental results showing the e ects of processing class files through our framework. In particular, we study the techniques necessary to effectively translate Jimple back to bytecode, without losing performance. Finally, we demonstrate that class file optimization can be quite e ective by showing the results of some basic optimizations using our framework. Our experiments were done on ten benchmarks, including seven SPECjvm98 benchmarks, and were executed on five di erent Java virtual machine implementations.

#### 1 Introduction

Java provides many attractive features such as platform independence, execution safety, garbage collection and object orientation. These features facilitate application development but are expensive to support; applications written in Java are often much slower than their counterparts written in C or C++. To use these features without having to pay a great performance penalty, sophisticated optimizations and runtime systems are required. For example, Just-In-Time compilers[1], adaptive compilers such as Hotspot<sup>TM</sup> and Way-Ahead-Of-Time Java compilers[18,17] are three approaches used to improve performance.

Our approach is to statically optimize Java bytecode. There are several reasons for optimizing at the bytecode level. Firstly, the optimized bytecode can then be executed using any standard Java Virtual Machine (JVM) implementation (interpreter, JIT, adaptive), or it could be used as the input to a

bytecode C or bytecode native-code compiler. Thus, the overall performance improvement is due to both our static bytecode optimization, and the optimizations and sophisticated runtime systems used in the virtual machines executing the optimized bytecode. Secondly, many di erent compilers for a variety of languages (Ada, Scheme, Fortran, Ei el, etc.) now produce Java bytecode as their target code. Thus, our optimization techniques can be applied as a backend to all of these compilers.

The goal of our work is to develop tools that simplify the task of optimizing Java bytecode, and to demonstrate that significant optimization can be achieved using these tools. Thus, we have developed the Soot[20] framework which provides a set of intermediate representations and a set of Java APIs for optimizing Java bytecode directly. Since our framework is written in Java, and provides a set of clean APIs, it should be portable and easy to build upon.

Early in our work we found that optimizing stack-based bytecode directly was, in general, too dicult. Thus, our framework consists of three intermediate representations, two of which are stackless representations. *Baf* is a streamlined representation of the stack-based bytecode, whereas *Jimple* and *Grimp* are more standard, stackless intermediate representations. Jimple is a three-address representation, where each instruction is simple, and each variable has a type. It is ideal for implementing standard compiler analyses and transformations. Grimp is similar to Jimple, but has aggregated expressions. Grimp is useful for decompilation, and as a means to generate ecient bytecode from Jimple.

In order to optimize bytecode we first convert bytecode to Jimple (the three-address representation), analyze and optimize the Jimple code, and then convert the optimized Jimple back to bytecode. In this paper we focus on the techniques used to translate from Jimple to e cient bytecode, and we give two alternative approaches to this translation.

Our framework is designed so that many di erent analyses could be implemented, above and beyond those carried out by javac or a JIT. A typical transformation might be removing redundant field accesses, or inlining. For these sorts of optimizations, improvements at the Jimple level correspond directly to improvements in final bytecode produced.

We have performed substantial experimental studies to validate our approach. Our first results show that we can indeed go through the cycle, bytecode to Jimple and back to bytecode, without losing any performance. This means that any optimizations made in Jimple will likely also result in optimizations in the final bytecode. Our second set of results show the e ect of optimizing class files using method inlining and a set of simple intraprocedural optimizations. These results show that we can achieve performance gains over a variety of Java Virtual Machines.

In summary, our contributions in this paper are: (1) three intermediate representations which provide a general-purpose framework for bytecode optimizations, and (2) a comprehensive set of results obtained by applying our framework to a set of real Java applications.

The rest of the paper is organized as follows. Section 2 gives an overview of the framework and the intermediate representations. Section 3 describes two alternative approaches to translating Jimple back to bytecode. Section 4 presents and discusses our experimental results. Section 5 discusses related work and Section 6 covers the conclusions and future work.

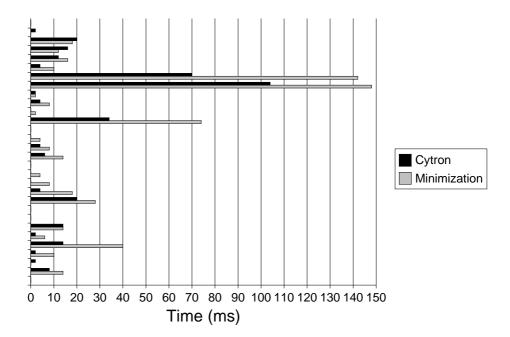

#### 2 Framework Overview

The Soot framework has been designed to simplify the process of developing new optimizations for Java bytecode. Figure 1 shows the overall structure of the framework. As indicated at the top of the figure, many di erent compilers can be used to generate the class files. The large box labeled SOOT demonstrates that the framework takes the original class files as input, and produces optimized class files as output. Finally, as shown at the bottom of the figure, these optimized class files can then be used as input to Java interpreters, Just-In-Time (JIT) compilers, adaptive execution engines like Hotspot $^{\rm TM}$ , and Ahead-of-Time compilers such as the High Performance Compiler for Java (HPCJ) $^{\rm TM}$  or TowerJ $^{\rm TM}$ .

The internal structure of Soot is indicated inside the large box in Figure 1. Shaded components correspond to modules that we have designed/implemented and each component is discussed in the following subsections.

# 2.1 Jimplify

The first phase is to *jimplify* the input class files, that is, to convert class files to the Jimple three-address representation. We convert to a three-address representation because optimizing stack code directly is awkward for several reasons. First, the stack implicitly participates in every computation; there are electively two types of variables, the implicit stack variables and explicit local variables. Second, the expressions are not explicit, and must be located on the stack[25]. For example, a simple instruction such as add can have its operands separated by an arbitrary number of stack instructions, and even by basic block boundaries. Another diculty is the untyped nature of the stack and of the local variables in the bytecode, as this does not allow analyses to make use of the declared type of variables. A fourth problem is the <code>jsr</code> bytecode. The <code>jsr</code> bytecode is dicult to handle because it is essentially a interprocedural feature which is inserted into a traditionally intraprocedural context.

We produce Jimple from bytecode by first processing the bytecode from the input class files and representing it in an internal format. During this translation jsr instructions are eliminated by inline expansion of code. After producing the internal form of bytecode, the translation to Jimple code proceeds as follows:

1. *Produce naive 3-address code*: Map every stack variable to a local variable, by determining the stack height at every instruction. Then map each instruction which acts implicitly on the stack variables to a 3-address code statement

$<sup>^{1}</sup>$  We currently use a tool called Co  $\,$  to achieve this translation.

Fig. 1. Soot Framework Structure

which refers to the local variables explicitly. For example, if the current stack height is 3, then the instruction iadd would be translated to the Jimple statement i2 = i2 + i3. This is a standard technique and is also used in other systems [18,17].

2. Type the local variables: The resulting Jimple code may be untypable because a local variable may be used with two di erent types in di erent contexts. Thus, we split the uses and definitions of local variables according to webs[16]. This produces, in almost all cases, Jimple code whose local variables.

ables can be given a primitive, class, or interface type.<sup>2</sup> To do this, we invoke an algorithm described in [9]. The complete solution to this typing problem is NP-complete, but in practice simple polynomial algorithms su ce. Although splitting the local variables in this step produces many local variables, the resulting Jimple code tends to be easier to analyze because it inherits some of the disambiguation benefits of SSA form[5].

3. Clean up the code: Jimple code must now be compacted because step 1 produced extremely verbose code[18,17]. We have found that simple aggregation (collapsing single def/use pairs) followed by copy propagation/elimination of stack variables to be su cient to eliminate almost all redundant stack variables.

Figure 2(a) shows an input Java program and Figure 2(b) shows the byte-code generated by javac as we would represent it in our Baf representation. Figure 2(c) shows the Jimple code that would result from jimplifying the byte-code. Note that all local variables have been given types. Variables beginning with \$ correspond to variables that were inserted to stand for stack locations, whereas variables that do not begin with \$ correspond to local variables from the bytecode.

### 2.2 Optimize Jimple

Most of the analyses and transformations developed by our group, as well as other research groups, are implemented using the Jimple representation. We have currently implemented many intraprocedural and interprocedural optimizations. In this paper we focus on studying the e ect of several simple intraprocedural techniques in conjunction with method inlining.

# 2.3 Convert Jimple Back to Stack Code

Producing bytecode naively from Jimple code produces highly ine cient code. Even the best JIT that we tested can not make up for this ine ciency. And it is very important that we do not introduce ine ciencies at this point that would negate the optimizations performed on Jimple.

We have investigated two alternatives for producing stack code, labeled Option I and Option II in Figure 1. These two options are discussed in more detail in Section 3, and they are experimentally validated in Section 4.

#### 2.4 Generate Jasmin Assembler

After converting Jimple to Baf stack code, the final phase is to generate Jasmin [11] assembler files from the internal Baf representation. Since Baf is a relatively direct encoding of the Java bytecode, this phase is quite simple.

<sup>&</sup>lt;sup>2</sup> Other cases must be handled by introducing type casts and/or introducing extra copy statements.

```

Object[] a;

int x;

public void f(int i, int c)

\{ g(x *= 10);

while(i * 2 < 10)

{ a[i++] = new Object();

}

(a) Original Java Source

.method public f(II)V

public void f(int, int)

aload_0

aload_0

Example this;

dup

int i, c, $i0, $i1, $i2, $i3;

getfield A/x I

java.lang.Object[] $r1;

bipush 10

java.lang.Object $r2;

imul

dup_x1

this := @this;

putfield A/x I

i := @parameter0;

invokevirtual A/g(I)V

c := @parameter1;

X:$i0 = this.x;

goto Label1

X:\$i1 = \$i0 * 10;

Label0:

this.x = $i1;

aload_0

this.g($i1);

getfield A/a [Ljava/lang/Object;

goto label1;

iload_1

iinc 1 1

label0:

new java/lang/Object

Y:$r1 = this.a;

$i2 = i;

i = i + 1;

invokenonvirtual

java/lang/Object/<init>()V

$r2 = new java.lang.Object;

aastore

specialinvoke $r2.<init>();

Y:$r1[$i2] = $r2;

Label1:

iload_1

label1:

iconst_2

Z:$i3 = i * 2;

imul

Z:if $i3 < 10 goto label0;</pre>

bipush 10

if_icmplt Label0

return;

}

return

(b) Bytecode

(c) Jimple

```

**Fig. 2.** Translating bytecode to Jimple

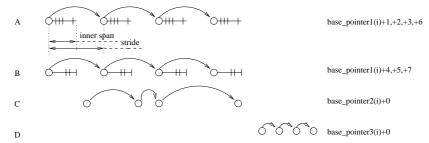

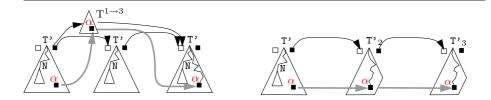

#### 3 Transformations

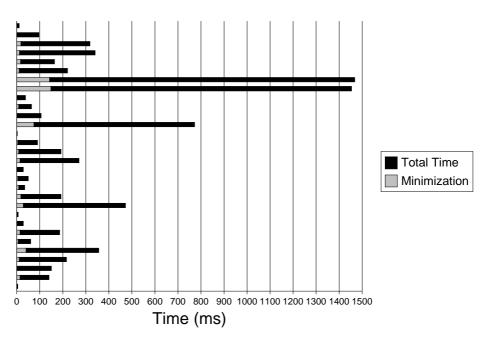

After optimizing Jimple code, it is necessary to translate back to e cient Java bytecode. Figure 3(a) illustrates the bytecode produced by a naive translation from Jimple.<sup>3</sup> Note that this naive code has many redundant store and load instructions reflecting the fact that Jimple computation results are stored to local variables, while stack-based bytecode can use the stack to store many intermediate computations.

<sup>&</sup>lt;sup>3</sup> Note that our Baf representation closely mirrors Java bytecode. However, we do streamline the representation somewhat and preserve the variable names as much as possible.

### 3.1 Option I: Produce Naive Baf and Optimize

The main idea behind Baf optimizations is to identify and eliminate redundant store/load computations. Figure 3(b) shows the results of applying the Baf optimizations on the naive code given in Figure 3(a).

The optimizations currently in use are all performed on discrete basic blocks within a method. Inter-block optimizations that cross block boundaries have also been implemented, but to date these have not yielded any appreciable speedups on the runtime and are not described here. In the following discussion it is assumed that all instructions belong to the same basic block.

In practice, the majority of the redundant store and load instructions present in naive Baf code belong to one of the following code patterns:

**store/load (sl pair)**: a store instruction followed by a load instruction referring to the same local variable with no other uses. Both the store and load instructions can be eliminated, and the value will simply remain on the stack.

store/load/load (sll triple): a store instruction followed by 2 load instructions, all referring to the same local variable with no other uses. The 3 instructions can be eliminated and a dup instruction introduced. The dup instruction replaces the second load by duplicating the value left on the stack after eliminating the store and the first load.

We can observe these patterns occurring in Figure 3(a) where labels A, B, C and E each identify distinct sl pairs, and where labels D and G identify sll triples.

To optimize a Baf method our algorithm performs a fixed point iteration over its basic blocks identifying and reducing these patterns whenever possible. By reducing, we mean eliminating an sl pair or replacing an sll triple to a dup instruction.

Reducing a pattern is trivial when all its instructions directly follow each other in the instruction stream. For example, the sl pairs at labels A and E in Figure 3(a) are trivial ones. However, often the store and load instructions are far apart (like at labels B and C.) To identify pairs of statements to reduce, we must determine the e ect on the stack of the intervening bytecode. These bytecodes are called the *interleaving sequences*.

We compute two pieces of information as a means to analyse interleaving sequences and their e ects/dependencies on the stack. The net e ect on the stack height after executing a sequence of bytecode is referred to as the *net stack height variation* or *nshv*. The minimum stack height variation attained while executing a sequence of bytecode is referred to as the *minimum stack height variation* or *mshv*. A sequence of instructions having both nshv = 0 and mshv = 0 is referred to as a *level sequence*.

If interleaving sequences are level sequences, then the target patterns can be reduced directly. This is because one can just leave the value on the stack, execute the interleaving instructions, and then use the value that was left on the stack. This is the case for the sl pair labeled B, and later the sl pair labeled C, once B has been reduced. Finally, the sll triple D can be reduced, once both B and C have been reduced. In general, however, many such interleaving sequences will not be level and no reductions will be possible without some reordering of the block's bytecode.

```

public void f(int, int)

{ word this, i, c, $i2, $r2;

this := Othis: Example;

i := @parameter0: int;

c := @parameter1: int;

public void f(int, int)

{ word this, i, c;

load.r this;

fieldget <Example: int x>;

A:store.i c;

this := @this: Example;

A:load.i c;

i := @parameter0: int;

push 10;

c := @parameter1: int;

mul.i;

load.r this;

G:store.i c;

F:load.r this;

F:load.r this;

F:load.r this;

G:load.i c;

fieldget <Example: int x>;

fieldput <Example: int x>;

push 10;

F:load.r this;

mul.i;

G:load.i c;

G:store.i c;

virtualinvoke

G:load.i c;

<Example: void g(int)>;

fieldput <Example: int x>;

goto label1;

G:load.i c;

virtualinvoke

label0:

<Example: void g(int)>;

load.r this;

goto label1;

fieldget

<Example: java.lang.Object[] a>;

label0:

B:store.r c;

load.r this;

load.i i;

fieldget

C:store.i $i2;

<Example: java.lang.Object[] a>;

inc.i i 1;

load.i i;

new java.lang.Object;

inc.i i 1;

D:store.r $r2;

new java.lang.Object;

D:load.r $r2;

D:dup1.r;

specialinvoke

specialinvoke

<java.lang.Object: void <init>()>; <java.lang.Object: void <init>()>;

B:load.r c;

arraywrite.r;

C:load.i $i2;

D:load.r $r2;

label1:

load.i i;

arraywrite.r;

push 2;

label1:

mul.i;

load.i i;

push 10;

push 2;

ifcmplt.i label0;

mul.i;

E:store.i $r2;

return;

E:load.i $r2;

push 10;

ifcmplt.i label0;

return;

}

(a) naive Baf generated from Jimple

(b) optimized Baf

```

Fig. 3. Optimizing Baf

If an interleaving sequence has nshv > 1 for a sll triple or nshv > 0 for a sl pair, then our algorithm will try to lower the nshv value by relocating a bytecode having a positive nshv to an earlier location in the block. This is illustrated by the movement of instructions labeled by F in Figures 3(a) and 3(b) in an attempt to reduce the pattern identified by G. Another strategy used when nshv < 0 is to move level subsequence ending with the pattern's store instruction past the interleaving sequence. Of course, this can only be done if no data dependencies are violated.

Applying these heuristics produces optimized Baf code which becomes Java bytecode and is extremely similar to the original bytecode. We observe that except for two minor di erences, the optimized Baf code in Figure 3(b) is the same as the original bytecode found in Figure 2(b). The di erences are: (1) the second load labeled by F is not converted to a dup; and (2) the pattern identified by G is not reduced to a dup\_x1 instruction. We have actually implemented these patterns, but our experimental results did not justify enabling these extra transformations. In fact, introducing bytecodes such as dup\_x1 often yields non-standard, albeit legal, bytecode sequences that increase execution time and cause many JIT compilers to fail.

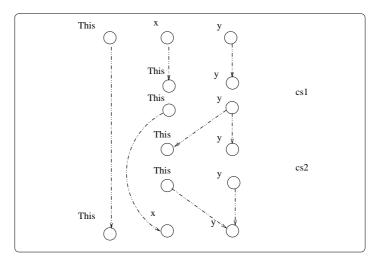

# 3.2 Option II: Build Grimp and Traverse

In this section, we describe the second route for translating Jimple into byte-code. The compiler javac is able to produce e cient bytecode because it has the structured tree representation of the original program, and the stack based nature of the bytecode is particularly well suited for code generation from trees[2]. Essentially, this phase attempts to recover the original structured tree representation, by building Grimp, an aggregated form of Jimple, and then producing stack code by standard tree traversal techniques.

Grimp is essentially Jimple but the expressions are trees of arbitrary depth. Figure 4(a) shows the Grimp version of the Jimple program in Figure 2(c).

**Aggregation of bytecode** The basic algorithm for aggregation is as follows. We consider pairs (def, use) in extended basic blocks, where def is an assignment statement with sole use use, and use has the unique definition def. We inspect the path between def and use, to determine if def can be safely moved into use. This means checking for dependencies and not moving across exception boundaries. We perform this algorithm iteratively, and the pairs are considered in reverse pseudo-topological order to cascade the optimizations as e ciently as possible. Examples of these aggregation opportunities are shown in figure 2(c) at the labels X, Y and Z. X and Z are trivial cases because their aggregation pairs are adjacent, but the pair at Y are a few statements apart. Thus before producing the aggregated code in 4(a) the interleaving statements must be checked for writes to this.a.

**Peephole optimizations** In some cases, Grimp cannot concisely express Java idioms. For example, the increment operation in a[i++] = new Object(); cannot be expressed, because Grimp only allows a definition to occur as the left-hand

```

public void f(int, int)

{ word this, i, c, $i2;

this := @this: Example;

i := @parameter0: int;

c := @parameter1: int;

load.r this;

fieldget <Example: int x>;

push 10:

public void f(int, int)

mul.i;

store.i c;

Example this;

int i, c, $i1, $i2;

load.r this;

load.i c;

this := @this;

fieldput <Example: int x>;

i := @parameter0;

load.r this;

c := @parameter1;

load.i c;

X:$i1 = this.x * 10;

virtualinvoke

this.x = $i1;

<Example: void g(int)>;

this.g($i1);

goto label1;

goto label1;

label0:

label0:

load.r this;

$i2 = i;

fieldget

<Example: java.lang.Object[] a>;

i = i + 1;

Y:this.a[$i2] =

load.i i:

inc.i i 1;

new java.lang.Object();

new java.lang.Object;

dup1.r

Z:if i * 2 < 10 goto label0;</pre>

specialinvoke

<java.lang.Object: void <init>()>;

arraywrite.r;

return;

}

label1:

load.i i;

push 2;

mul.i

push 10;

ifcmplt.i label0;

return;

(b) Baf generated from Grimp

(a) Grimp

```

Fig. 4. Generating Baf from Grimp

side of an assignment statement, not as a side e ect.<sup>4</sup> To remedy this problem, we use some peephole optimizations in the code generator for Grimp.

For example, for the increment case, we search for Grimp patterns of the form:

```

s1: local = <lvalue>;

s2: <lvalue> = local/<lvalue> + 1;

s3: use(local)

```

and we ensure that the local defined in  $s_1$  has exactly two uses, and that the uses in  $s_2$ ,  $s_3$  have exactly one definition. Given this situation, we emit code for only  $s_3$ . However, during the generation of code for  $s_3$ , when local is to

<sup>&</sup>lt;sup>4</sup> This design decision was made to simplify analyses on Grimp.

be emitted, we also emit code to duplicate local on the stack, and increment <lvalue>. An example of this pattern occurs just after LabelO in Figure 4(a).

This approach produces reasonably e cient bytecode. In some situations the peephole patterns fail and the complete original structure is not recovered. In these cases, the Baf approach usually performs better. See the section 4 for more details

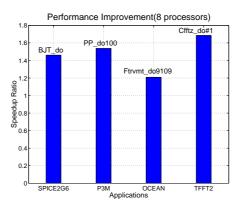

# 4 Experimental Results

Here we present the results of two experiments. The first experiment, discussed in Section 4.3, validates that we can pass class files through the framework, without optimizing the Jimple code, and produce class files that have the same performance as the original ones. In particular, this shows that our methods of converting from Jimple to stack-based bytecode are acceptable. The second experiment, discussed in Section 4.4, shows the e ect of applying method inlining on Jimple code and demonstrates that optimizing Java bytecode is feasible and desirable.

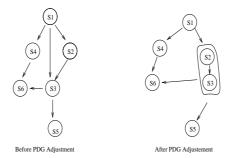

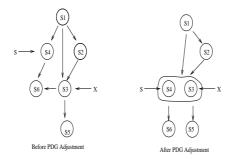

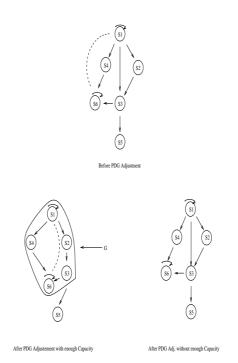

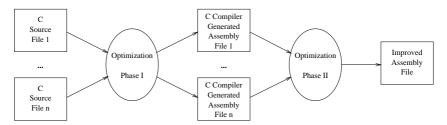

# 4.1 Methodology